|

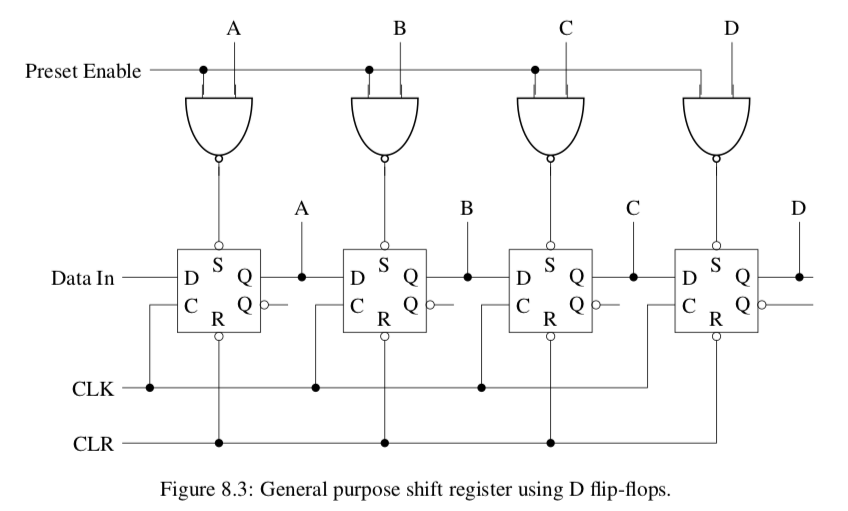

The D pin is an input/output pin since we willīe using it as both an input and output since we are cascading D flip flops.ģ. This D flip flop symbol omitting the Clk’ as a pinīecause we do not need it after this step. Then I created the D flip flop using the symbols I madeĪs my inputs. To make the design easier to look at, I created individualĬells for the inverter and the transmission gate and made symbols for them.ĭ-FLIP FLOP SYMBOL USING TRANSMISSION GATE SYMBOLĢ. The first thing I did was create a D-FLIP FLOP using transmission A D flipįlop is created using inverters and transmission gates.ġ. Register, and the hold register are made up of eight D flip flops. Input value and the original clock value divided by eight. Is made up of a shift register that reads in a D input value and a clock value,Īnd a hold register that reads in the output of the shift register as the D Schematic overview: a serial to parallel converter

Transistor sizes: NMOS and PMOS both 6u/600n Input is 10Mbits/s then the parallel output is 1.25MWords/s.Ĭonsists of schematics, simulations and layout. Signal and a clock signal and creates an 8-bit parallel word and clock.

Is the design of a serial-to-parallel converter that takes a serial input

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed